## FSM based tests' fault coverage for the gate-level circuit design

#### Evgeny Vinarsky Moscow State University Under the framework of the French-Russian Lab QUALIPSO

Paris 2016

### Motivation

- Hardware testing is important...

- Different abstraction levels:

- FSM / Automata models can be used for this

- Tests can be derived from the logic circuits directly

The question arises: what is the relationship between tests derived for an FSM and a logic circuit which describe the same digital system?

## FSM based tests VS logic circuit based tests

| FSM tests:                                                           | Logic circuit based tests:                                          |

|----------------------------------------------------------------------|---------------------------------------------------------------------|

| Are derived at the <u>high</u> level of abstraction when designing a | Are derived at the <u>low</u> level of abstraction when designing a |

| digital device                                                       | digital device                                                      |

| Have a set of well developed                                         | Have a set of well developed                                        |

| Black Box techniques for the                                         | White Box test derivation                                           |

| test derivation                                                      | techniques                                                          |

| Detect transition and output                                         | Usually "take care" of Single                                       |

| faults in the implemented                                            | Stuck-at Faults, Bridges, etc.                                      |

| system                                                               | that can occur at the logic level                                   |

Problem statement : Are FSM tests good enough for detecting faults at the logic circuit level?

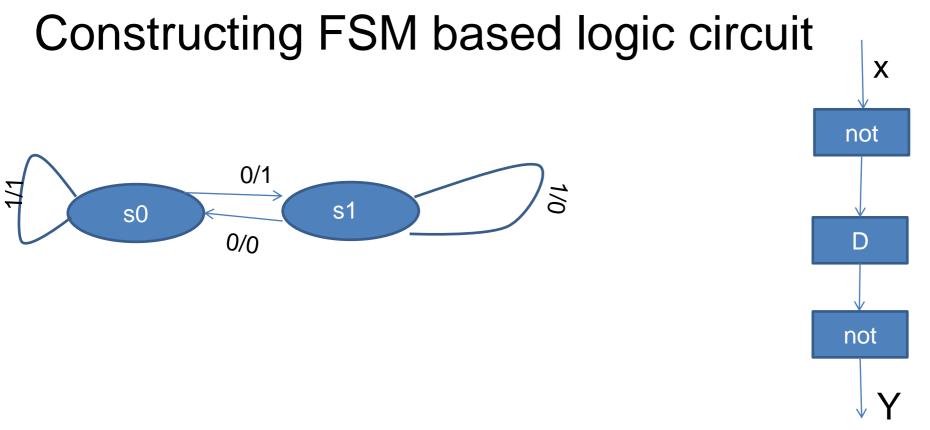

- Given an FSM, in order to derive a corresponding logic circuit, we encode each state, input and output with a Boolean vector

- Transition and output FSM functions become Boolean functions and we implement them by the composition of logic gates and latches

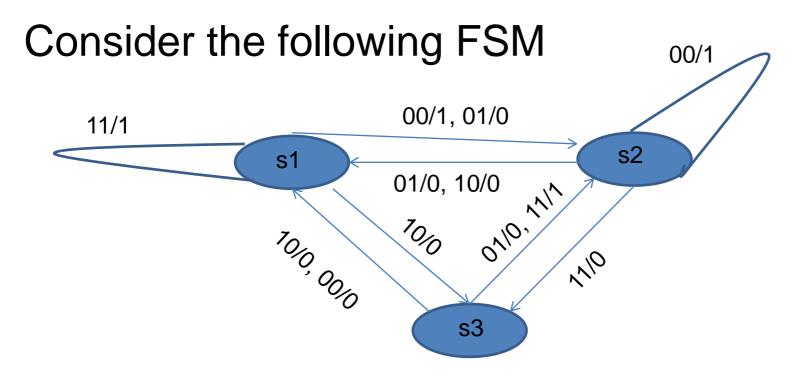

## Checking FSM tests

Given an FSM and a corresponding logic circuit

- We derive the transition tour

- And check whether simple logic faults can be detected by the transition tour

For this purpose we...

- Randomly generated FSMs with small number of states and corresponding transition tours

- Derived a corresponding logic circuit

- Randomly replaced a single gate with another gate

- Checked if this fault can be detected by the transition tour

Fast enough we have found an example when a logic fault is not detected

#### Example

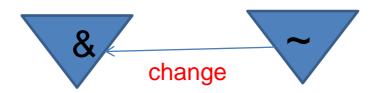

# What if the circuit is implemented wrongly?

In this mutant, an AND gate is replaced with the XNOR gate

Applying the test sequence, we obtain the expected output response

The fault is not detected ⊗

But this bug can be detected by another input sequence

Conclusion: FSM based tests not always detect bugs at the logic circuit level

#### Conclusions

FSM based tests do not kill some logic level mutants We don't know if logic level based tests can kill all/some FSM mutants

Digital device design should address different types of tests at different abstraction levels

#### Future work :

To study necessary/sufficient conditions when FSM based tests can guarantee the fault coverage over the logic level circuits To perform some experiments to estimate the corresponding fault coverage

# Thank you for your attention!

$\dots$  and for the grant for my participation  $\odot$